1.1.7 声明导线

题目描述

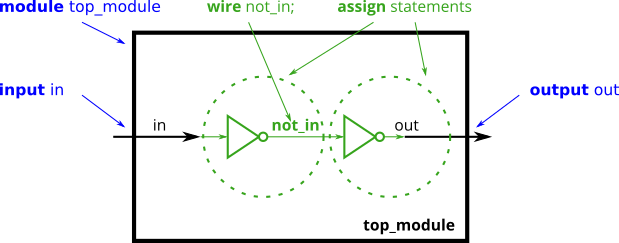

迄今为止的电路都比较简单,输出是输入的简单函数。随着电路变得越来越复杂,你需要使用导线来连接内部组件。当需要用到导线时,应该在模块体中,在首次使用之前声明它。(将来,你会遇到更多类型的信号和变量,它们也是以同样的方式声明的,但目前,我们先从wire类型信号开始。)

示例

module top_module (

input in, // Declare an input wire named "in"

output out // Declare an output wire named "out"

);

wire not_in; // Declare a wire named "not_in"

assign out = ~not_in; // Assign a value to out (create a NOT gate).

assign not_in = ~in; // Assign a value to not_in (create another NOT gate).

endmodule // End of module "top_module"

在上述模块中,共有三条导线(in、out 和 not_in),其中两条作为模块输入和输出端口的一部分已经被声明(这就是为什么在之前的练习中你不需要声明任何导线的原因)。导线not_in需要在模块内部声明。它在模块外部是不可见的。然后,使用两个assign语句创建了两个非门。注意,你先创建哪个非门并不重要:最终得到的电路是相同的。

实践

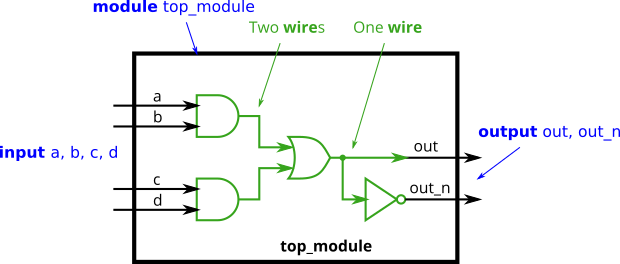

实现以下电路。创建两个中间导线(命名随意)来连接与门和或门。请注意,供给非门的导线实际上是out导线,因此在这里你不一定需要声明第三条导线。注意导线是由唯一一个源(门的输出)驱动的,但可以供给多个输入使用。

如果你按照图中的电路结构进行,你应该最终得到四个assign语句,因为有四个信号需要被赋予值。

(是的,不使用中间导线也有可能创建具有相同功能的电路。)

模块声明

`default_nettype none

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );